Mentor Graphics Modelsim Se-64 2019.2 (x64) | 899 MB

Information:

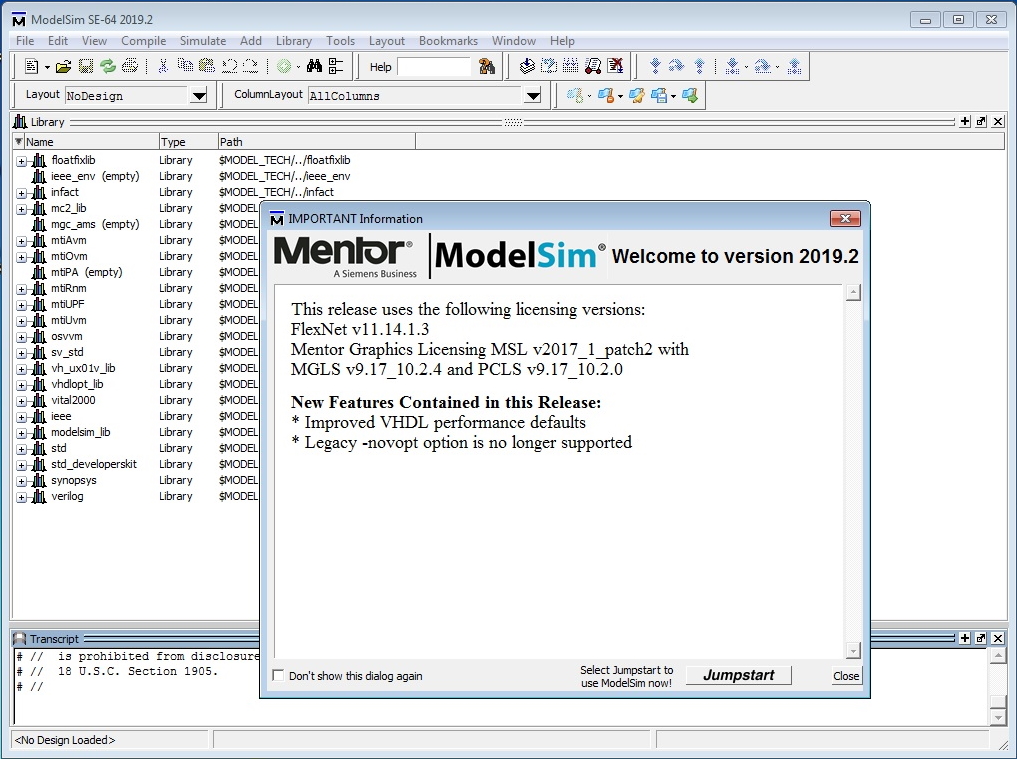

Mentor, a Siemens business, is pleased to announce the availability of ModelSim 2019.2, is unified debug and simulation environment gives today’s FPGA designers advanced capabilities in a productive work environment.

Modelsim HDL simulator provides FPGA customers with and easy cost-effective way to speed up FPGA development, lab bring up and test. Many FPGA designers go to the lab before adequately vetting their design. This means weeks or even months of inefficient debugging time in the lab. Testing in the lab has limited visibility of the signals in design. It can take 8 hours to do a place and route just instrument additional signals or make a small bug fix. With simulation the debug loop is much faster and there is complete visibility into the signals in the design. Simulation enables a much higher quality FPGA design before entering the lab allowing time spent during lab debug much more productive and focused.

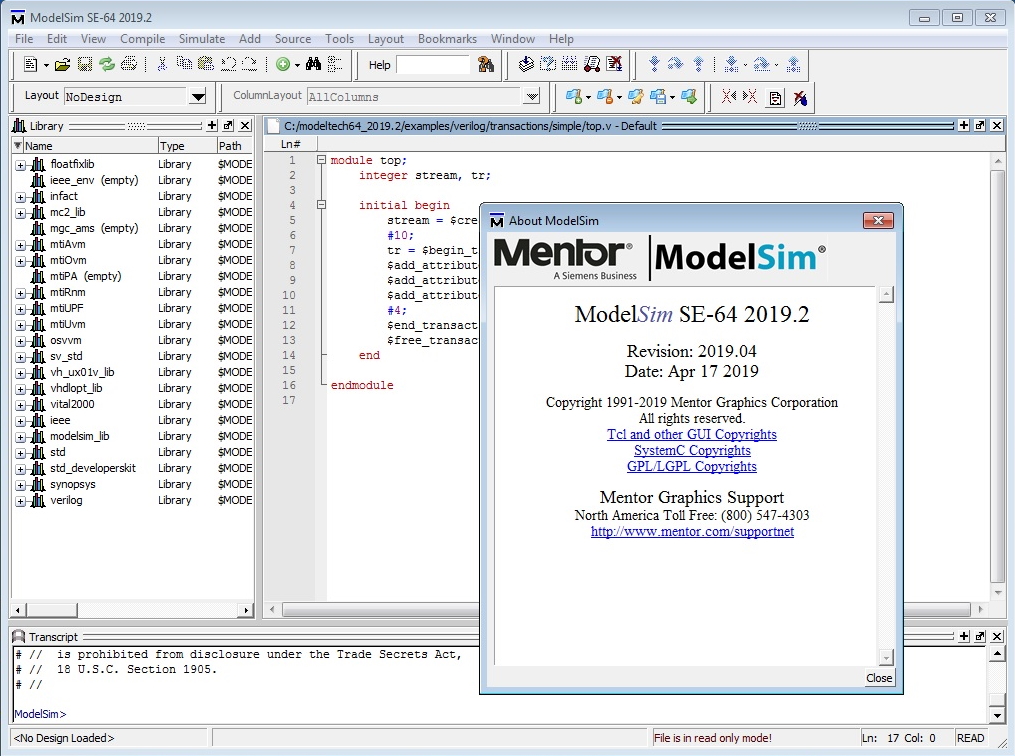

In addition to supporting standard HDLs, ModelSim increases design quality and debug productivity. ModelSimâs award-winning Single Kernel Simulator (SKS) technology enables transparent mixing of VHDL and Verilog in one design. Its architecture allows platform-independent compile with the outstanding performance of native compiled code.

The graphical user interface is powerful, consistent, and intuitive. All windows update automatically following activity in any other window. For example, selecting a design region in the Structure window automatically updates the Source, Signals, Process, and Variables windows. You can edit, recompile, and re-simulate without leaving the ModelSim environment. All user interface operations can be scripted and simulations can run in batch or interactive modes. ModelSim simulates behavioral, RTL, and gate-level code, including VHDL VITAL and Verilog gate libraries, with timing provided by the Standard Delay Format (SDF).

Mentor Graphics Corporation is a world leader in electronic hardware and software design solutions, providing products, consulting services and award-winning support for the worlds most successful electronic, semiconductor and systems companies. Established in 1981, the company reported revenues in the last fiscal year in excess of $1.15 billion. Corporate headquarters are located at 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777.

Website Home Page :

Code:

http://nitroflare.com/view/B94D6906255D5A0/Meera169_Mentor_Graphics_Modelsim_Se-64_2019.2_x64.rar